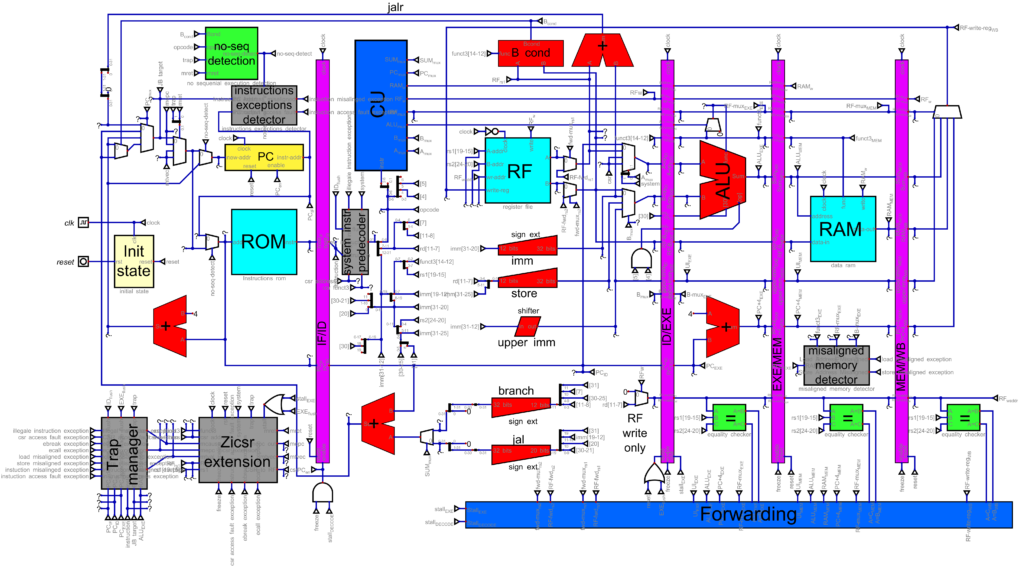

Ce projet open source est l’implémentation à partir de la base, du célèbre processeur moderne et en vogue RISC-V, se basant sur une micro-architecture en pipeline permettant d’accroître la vitesse d’exécution des instructions. Plus précisément, c’est l’amélioration de la précédente implémentation du même processeur en single-cycle RISC-V 1C. La particularité de cette implémentation en comparaison avec d’autres implémentations sur le net, c’est que c’est une implémentation visuelle (vous pouvez voir son diagramme sur l’image en bas) et non textuelle (sous forme de code), pédagogique sur le simulateur logique Digital de Helmut Hneemann, avec un code couleur et une mise en disposition organisée de telle sorte à faciliter le suivi du flux des signaux dans les composantes internes du processeur lors de son exécution, et même une exécution pas à pas avec un accès total à toutes les entités internes du processeur. Sachant cela, il est aussi tout à fait possible de générer du code Verilog ou VHDL par le simulateur permettant l’intégration les outils classiques de développement du hardware. D’ailleurs le code source (légèrement modifié) du processeur en Verilog est ajouté à ce projet. Il est aussi tout à fait possible d’implanter ce processeur sur FPGA pour avoir une réalisation physique réelle de ce dernier.

Le processeur peut être décrit comme un processeur en pipeline en 5 étages RISC-V RV32I, c’est un processeur 32 bits avec les opérations sur les entiers. L’ensemble des instructions implémentées sont présentées sur la table en bas. Le processeur n’implémente que le mode machine (m-mode), incluant les instructions privilégiées due l’extension Zicsr (CSRRW, CSRRS, CSRRC, CSRRWI, CSRRSI, CSRRCI) et autres instructions privilégiées comme ECALL, EBREAK, MRET, WFI.

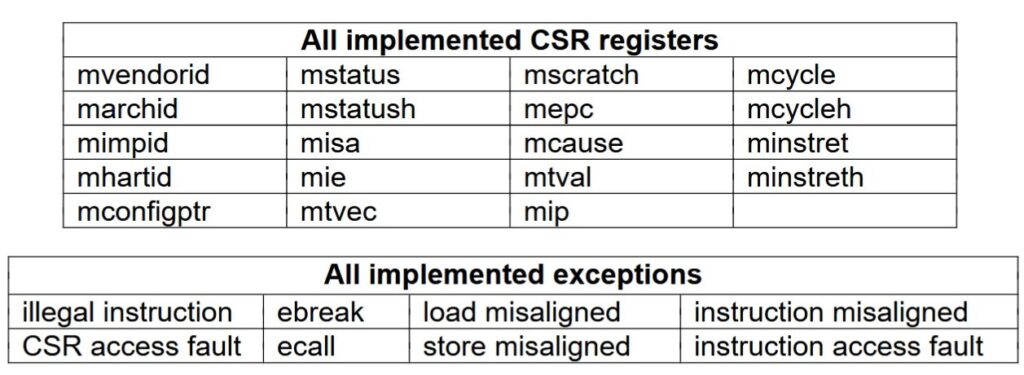

Les registres CSR les plus importants sont implémentés, la liste de tous les registres implémentés est sur le tableau en bas. Le mécanisme de trap est implémenté pour les interruptions et les exceptions, les connections d’interruption sont accessibles mais aucun gestionnaire d’interruption n’est implémenté. Par contre les exceptions les plus connues sont implémentées. La liste de toutes les exceptions est visible sur le tableau en bas.

Implémentation

Comme vous pouvez le voir sur le datapath (sur la première image en haut), le processeur est structuré autour des 5 étages standards d’un processeur pipeline, IF, ID, EXE, MEM, WB. Pour plus de clarté, un code couleur est utilisé pour distinguer les fonctionnalités des composants du processeur. Par exemple, les 4 bars en violé représentent les registres tampons de séparation entre les étages du pipeline. Les composants en rouge représentent les unités arithmétique, comme l’ALU, les additionneurs, les détendeurs de signe, un shifteur, et un comparateur (le B cond, pour Branch Condition). Les multiplexeurs sont en blanc, ainsi que les portes de collage. En bleu clair les mémoires, comme la ROM, la RAM, et le Register File (RF). La couleur bleue représente les unités de contrôle, le CU et le gestionnaire de forwarding. En vert, se sont les unités de gestion de Hazard. Le Program Counter en jaune. Les unités en gris sont responsables du mode privilégié comme l’implémentation de l’extension Zicsr et le gestionnaire de trap.

L’implémentation du pipeline est relativement complexe, cela suscite implicitement l’utilisation de beaucoup d’autres techniques sous-jacentes comme le feed forwarding, stalling, branch prediction, pipeline flushing, hazard handling.

Tests et validation

Pour s’assurer que le processeur fonctionne correctement en suivant les spécifications officielles par l’organisme RISC-V, nous avons décidé de choisir la suite de tests officielle de proposée par l’organisme nommée suite riscv-tests. Il s’agit d’un ensemble de tests unitaires conçus pour vérifier la correction fonctionnelle des implémentations de l’architecture RISC-V, plus précisément son jeu d’instructions. Ces tests en assembleur vérifient la conformité des instructions à l’architecture privilégiée RV32I afin de garantir que le processeur conçu correspond aux spécifications RISC-V. Le processeur RISC-V 5P arrive effectivement à passer les tests avec succès. Sauf pour l’instruction fence.i qui n’est pas implémentée, et le désalignement mémoire que nous avons préféré une gestion logicielle plus simple, que matérielle.

Performance et benchmark

Le test de performance utilisé pour évaluer le processeur RISV-V 5P est appelé Dhrystone. C’est en effet, un banc d’essai classique (ou Benchmark en anglais) de calcul pour mesurer les performances en calcul entier et l’efficacité de la programmation système sur le processeur. Plutôt célèbre pour l’évaluation des processeurs de petite empreinte et les processeurs pour les Systèmes embarqués et l’Internet of Things (IoT). L’unité de mesure de Dhrystone est généralement exprimée en Dhrystone MIPS (DMIPS), souvent normalisés par MHz de fréquence d’horloge exprimée en DMIPS/MHz. Le résultat du benchmark sur le RISC-V 5P est de 1.32 DMIPS/MHz, ce qui est franchement pas mal. En comparaison le processeur basique d’Arduino est approximativement 0.3 DMIPS/MHz par exemple.

Dépôt GitHub

Plus de détails et tout le code source et les circuits du processeur, ainsi que les fichiers nécessaires pour la compilation sur FPGA. Sont disponible sur le dépôt GitHub : https://github.com/kara-abdelaziz/RISC-V-5P